Baugruppentest mittels Flying-Probe-Tester

Reduzierung der Testzeit und Steigerung der Prüfschärfe

Im Entwicklungs- und Fertigungsprozeß elektronischer Produkte ist die Time-to-Market entscheidend für eine erfolgreiche Vermarktung. Insbesondere der Übergang von der Entwicklung zur Fertigung kann zu unerwünschten Verzögerungen fuhren. Ursache dafür ist einerseits die Vielfalt möglicher Fehler (Konzept, Hardware, Software, Fertigung) und andererseits die für die Fehlerlokalisierung benötigte Zeit.

1. Benachbarte Leitungen

2. Die Grundkonzeption

des Netztests

3. Durch den Netztest abgedeckte

Fehlerarten

4. Netztest-Implementierung

5. Wann ist der Flying-Probe

Test eine wirtschaftliche Alternative?

6. Wirtschaftlichkeitsbetrachtungen

7. Zusammenfassung

Prüftechnik-Dienstleistungen

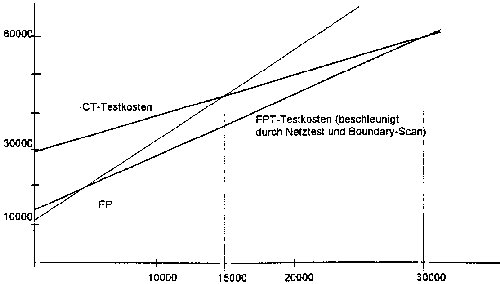

Beispiel für den Vergleich der Testkosten beim In-Circuit-Test (ICT)

und

beim Flying-Probe-Test (FPT)

Zugrundeliegende Basisdaten:

| Testkosten (Tester) | 100 DM / Stunde | |

| Investition ICT | 30000 DM (Adapter + Programm) | |

| Investition FPT | 12000 DM (Prüfprogramm) | |

| Investition FPT + Boundary-Scan |

15000 DM | |

| Laufzeit ICT | 30 sec | |

| Laufzeit FPT | 65 sec | |

| Laufzeit FPT mit Boundary-Scan |

45 sec | |

| Anzahl Netze | 500 | |

| Testzeit/Netz am FPT | 0,13 sec | |

Einen wichtigen Fortschritt bei Diagnose und Separierung der Fertigungsfehler von anderen Fehlerquellen in dieser Phase konnte man mit dem Aufkommen von Flying-Probe-Testern erzielen. Der Kostenvorteil dieser Test-methode im Vergleich zum In-Circuit-Test ergibt sich hauptsächlich durch den Verzicht auf Adapter, durch kürzere Prüfprogramm-Erstellungszeiten und die sehr wichtige Flexibilität in Bezug auf die Benadelung. Daraus resultieren auch die niedrigeren Kosten in der Phase der Produktstabilisierung.

Das Prinzip des Flying-ProbeTesters beruht auf der seriellen Abfolge der Nadelbewegungen und der entsprechenden Testschritte. Deshalb ist die Testzeit von der Anzahl der Netze und der Elemente (R,L,C) abhängig. Der Umstieg auf einen In-Circuit-Tester lohnt sich erst dann, wenn die geplante Stückzahl hoch genug ist oder Logik und physikalischer Entwurf des Elektronikprodukts so stabil sind, daß kein Redesign zu erwarten ist. Ein Verbleiben am FlyingProbe-Tester ist somit auch in der Fertigung oft eine wirtschaftliche Alternative. Das gilt dann, wenn die geplante Stückzahl weiterhin niedrig ist, eine Stückzahl-planung nicht möglich oder unsicher ist, die Wahrscheinlichkeit für ein Redesign im Laufe der Produktion hoch ist oder die Testzeit am Flying-Probe-Tester im Vergleich zum In-Circuit-Tester relativ kurz ist.

Im folgenden wird ein Verfahren vorgestellt, mit dem die Testzeit im Vergleich zur Standardmethode erheblich verkürzt werden kann. Außerdem erhöhen die angewendeten Meßkonzepte die Fehlerabdeckung für Short- und Open-Fehler. Dazu bieten die Informationstechnischen Dienstleister der Siemens AG in München-Perlach entsprechende Dienstleistungen an.

BENACHBARTE LEITUNGEN

Der Standardtest am Flying-Probe-Tester umfaßt den Diodentest sowie den Elementetest (R, L, C, D) und den Kurzschluß-oder Short-Test. Bestimmend für die Prüfzeit ist meist der Short-Test. Dazu ist insbesondere festzustellen, daß die Anzahl der Short-Prüfschritte direkt abhängig ist von der Anzahl der benachbarten Leitungen. Diese Zahl und somit auch die Testzeit hängen von der Definition der ,,Nachbarschaft" ab, die wiederum meistens auf einer programmierbaren maximalen Entfernung D beruht. Je höher D, umso besser ist die Fehlerabdeckung - aber mit D steigt auch die Testzeit. Es soll hier nicht auf die Komplexität der beiden Relationen (Abhängigkeit der Fehlerabdeckung und Testzeit von D) eingegangen werden; jedoch sollen die Risiken aufgezeigt werden. Ist D zu niedrig, ergibt sich eine niedrige Fehlerabdeckung, ist D zu hoch, resultiert eine zu lange Testzeit.

Ein Optimum für D kann nur durch eine Fehlerstatistik ermittelt werden; das heißt, daß zumindest in der Anfangsphase noch keine optimale Prüfschrittmenge für den Short-Test angewendet wird. Durch die erhöhte Prüfschärfe der nachfolgend dargelegten Vorgehensweise wird dieses Problem gelöst. Der Netztest reduziert die Prüfzeit und erhöht die Fehlerabdeckung.

DIE GRUNDKONZEPTION DES NETZTESTS

Die Grundkonzeption des Netztestes beruht auf der Tatsache daß die Netze A und B mit lmpedanz XA und XB im Kurzschlußfall einen Wert (XA*XB) I (XA+XB) aufweisen. Eine der beiden Abweichungen vom Sollwert

und

und

beträgt mindestens 50% und ist somit ohne hohe Genauigkeitsansprüche am Testsystem erkennbar. Die weiteren Details des Verfahrens können bedingt durch ihren Umfang und ihre Komplexität an dieser Stelle nicht vertieft werden.

Neben der beschriebene Problematik waren auch die beachtliche Anzahl der benachbarten Netze (empirische Werte: drei bis 14 Netze/Netz) und somit der hohe Anteil der Short-Testschritte Beweggründe für die Zielsetzung: Es soll mit einer Kontaktierung pro Netz (die je nach Bedarf bis zu vier Meßschritte beinhaltet) die Short-Testzeit reduziert und außerdem die Fehlerabdeckung erhöht werden. Zugleich soll auf die Kontaktierung der benachbarten Leitungen verzichtet werden. Unterstützt durch umfangreiche Untersuchungen am Flying-Probe-Tester APT8400 konnte nachgewiesen werden, daß mit den Netzmessungen gegen Ground der Größen

- UD = f(I) Diodenverhalten des Netzes

- C = f(UAC) AC-Verhalten (Kapazitätsverhalten)

- R = f(UDC) DC-Verhalten (Widerstand)

diese Zielsetzung realisierbar ist.

In Bezug auf die linearen und nichtlinearen Kennlinien getesteter Netze können sechs Netztypen gebildet werden. Mit der gezielten Stimuli-Anwendung von DG- und AG-Stimuli-Quellen des Testers konnte die Kurzschlußfrejheit eines jeden Netzes einwandfrei festgestellt werden (Verfahren ist patentiert). Im Kurzschlußfall liegt immer mindestens eine Istgröße an mindestens einem der beteiligten Netze außerhalb des Sollbereichs.

Wie bereits erwähnt, wird durch den Netztest das R-Verhalten (Widerstand), das L/C-Verhalten (Kapazität / Induktivität) und das D-Verhalten (Diode/Transistor) an jedem Netz getestet. Somit werden außer dem Short-Test zwischen zwei beliebigen Leitungen noch folgender Fehler erkannt: IC-Opens; wenn ein IC-Pin/ Netz oder ein interner Widerstand im IC vorhanden ist, und interne Impendanzen (beispielsweise ein Widerstand) im IC (maßgebend für die Erhöhung der Prüfschärfe im Vergleich zur Standardlösung) sowie alle gegen Potential / Ground angeschlossenen Elemente (R, L, C D), deren Anteil: 50 bis 90% beträgt. Außerhalb des Netztests werden nur die potentialfreien Elemente (kein Anschluß gegen Potential) geprüft.

DURCH DEN NETZTEST ABGEDECKTE FEHLERARTEN

An einem Flying-Probe-Tester mit vier Nadeln können gleichzeitig drei Netze kontaktiert und getestet werden. Die vierte Nadel ruht während der Testphase auf Ground. Ein homogener Test mit sehr kurzen Wegen ergibt sich durch Sortieren der Netz-Kontaktierungspads (nach x und y). So kann man beispielsweise ein 20 mm breites Segment von unten nach oben testen und anschließend von oben nach unten. Erfahrungswerte am APT8400 für die Testzeit liegen bei 0,1 bis 0,16 s/Netz. Beim Standardverfahren wurden Werte von 0,5 bis 1 s/Netz festgestellt.

NETZTEST-IMPLEMENTIERUNG

Der Go/No-go-Test beinhaltet den Netz-test und den Test der nicht an Potential angeschlossenen Elemente. Im Short-Fehlerfall werden für die beteiligten Netze nach dem Standardverfahren zusätzlich die benachbarten Netze geprüft, um eine genaue Diagnose zu ermöglichen. Diese Vorgehensweise erfordert nur noch wenige Sekunden pro Fehler zusätzlich. Bei einer Fertigungsqualität von beispielsweise 90% werden die Diagnoseschritte an 2 bis 5% der Baugruppen angewendet. Die Standard-Short-Prüfschritte stellen also den passiven Bestandteil des Prüfprogramms dar. Für diesen Diagnose-Short-Test kann die Nachbarschaft der Netze relativ großzügig definiert werden (Radius D hoch), da diese Prüfschritte im Go-Fall keinen Einfluß auf die Testzeit haben.

WANN IST DER FLYING-PROBE-TEST EINE WIRTSCHAFTLICHE ALTERNATIVE?

Die Gleichheit der Gesamtkosten für beide Testmethoden ergibt sich

aus:

(KAD + KI)+TI

* KIS = KF+TF

* KFS * n

Daraus ergibt sich der Grenzfall bei der Stückzahl:

![]()

Für jede-Stückzahl n < n0 ist

der Flying-Probe-Test eine kostengünstigere

Altemative, so daß zusätzlich zum Prototypentest die Anwendung

des Flying-ProbeTesters auch in die Fertigungsphase hinein sinnvollerweise

verlängert werden kann. Ursache dafür ist die Kostenhürde,

bedingt durch zusätzliche Prüfprogramme und Adapterkosten (KAD

+ KI).

WIRTSCHAFTLICHKEITSBETRACHTUNGEN

Aufgrund des Vergleichs der Testzeiten für Standardverfahren und Netztest ist eine Verschiebung des Break-Even-Point zugunsten des Flying-Probe-Testverfahrens zu erwarten. Die wesentlichen Parameter für die Kostenbestimmung bei beiden Testmethoden sind:

| n | geplante Baugruppenanzahl pro Typ | |

| KF | Prüfprogrammkosten für Flying-Probe-Tester | |

| KFS | Standkosten für Flying-Probe-Tester (Personal + Tester / Zeiteinheit) | |

| TF | Verweilzeit am Flying-Probe-Tester KAD = Adapterkosten für In-Circuit-Test | |

| KI | Prüfprogrammkosten für In-CircuitTest | |

| TI | Verweilzeit am In-Circuit-Test | |

| KIS | Standkosten für Jn-Circuit-Test | |

Für jede Stückzahl n < no ist der FlyingProbe-Test eine kostengünstigere Alternative, so daß zusätzlich zum Prototypen-test die Anwendung des Flying-Probe-Testers auch in die Fertigungsphase hinein sinnvollerweise verlängert werden kann. Ursache dafür ist die Kostenhürde, bedingt durch zusätzliche Prüfprogramme und Adapterkosten (KAD + KI).

Unter der Annahme daß

| KAD | 10.000 DM | |

| KF | 10.000 DM | |

| KI | 15.000 DM | |

| KIS=KFS | 100 DM/Stunde | |

| TI | 10 sec | |

| tnetz | 0,13 sec | |

betragen, wird die Stückzahl n0 in Abhängigkeit der Netzanzahl dargestellt.

ZUSAMMENFASSUNG

Mit Hilfe des Netztests kann am FlyingProbe-Tester eine erhebliche Reduzierung der Testzeit und eine Erhöhung der Prüfschärfe erreicht werden. Im Vergleich zum Standardverfahren ergaben sich folgende Effekte, die zur Reduzierung der Testzeit führen. Es ist nur eine Kontaktierung je Netz notwendig. Außerdem ist der Test von drei Netzen gleichzeitig an einem Vier-Nadel-Tester möglich. Maßgebend für die Erhöhung der Prüfschärfe ist die Erfassung von Opens für IC-Pins mit einer definierten Impedanz im Baustein (Standard: Netze mit einem ICPin) und die Abdeckung aller Kurzschlüsse (Standard:Kurzschlüsse mit benachbarten Netzen).

Eine weitere Verschiebung der Wirtschaftlichkeitsgrenze zu höheren Baugruppenstückzahlen zugunsten des Flying-ProbeTesters liegt im zunehmenden Einsatz des Boundary-Scan-Verfahrens begründet. Die Voraussetzung dafür ist die Integration des Boundary-Scan-Moduls in den FlyingProbe-Tester. Die beschriebene Vorgehensweise zeigt somit den Trend zu verstärktem Einsatz von Flying-Probe-Tester kombiniert mit Netztest-Methode und Boundary-Scan nicht nur für den Prototypen-Test sondern auch in der Serie.

PRÜFTECHNIK-DIENSTLEISTUNGEN

Die in diesem Beitrag beschriebenen Techniken werden von den Informationstechnischen

Dienstleistern der Siemens AG als Dienstleistungen für Prüftechnik-Abteilungen

angeboten.